# More than the Machine – **Using Memristors for Computing**

Dietmar Fey Department Computer Science -Chair for Computer Architecture Friedrich-Alexander-University Erlangen-Nürnberg

Who is aware of HP's Machine?

FRIEDRICH-ALEXANDER UNIVERSITY

Utilisation of different technologies

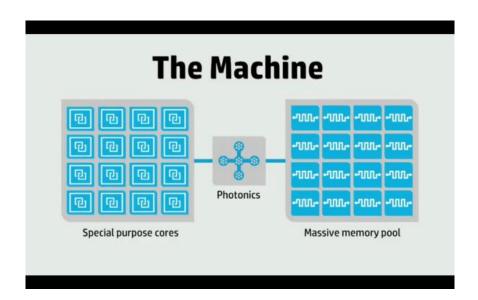

# Electrons for compute

Electrons like to interact; easily moved; interaction needed for compute

+ lons for storage

lons like to interact; stay put; good for storage

+ Photons to communicate

Photons don't like to interact or stay put; good for long-distances

Courtesy: Jouppi2011

**Architecture**

Source: P. Ranganathan, "Saving the world together, one server at a time..." ACACES 2011

- Special purpose cores arbitrarily connected with pool of non-volatile memories – the memristors

- Access times between 0.3 and 3 ns (< below 250 ns)</li>

- Mostly flat memory model

- Paging and TLBs shall become obsolete

- Vision: Cache becomes non-volatile

- What is the Machine?

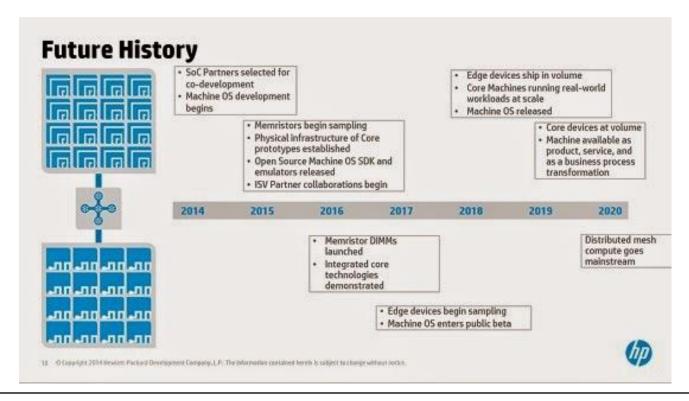

- HP will provide first products of a complete new computer architecture within the next two to three years

**FUTURE COMPUTING 2015,**

Nice, 23th March, 2015.

Slide 5

Key note "more than the Machine -

**Using Memristors for Computing"**

Up 160 racks based on memristors connected to a cluster

Data capacity up to 160 Petabyte

Size of a refrigerator

- Processor cores and memory connected via high speed fiber optics

- Bandwidth of 6 Terabit / second

- Machine rack no server

- Architecture flexible configurable from mobile device up to large computer

- Schedule for the revolution

- New memory controllers

- New OS for the Machine: Linux++ → Carbon

#### **Outline**

- Memristor technology

- Digital Boolean logic with memristors

- Ternary Computing using memristors

- Conclusion

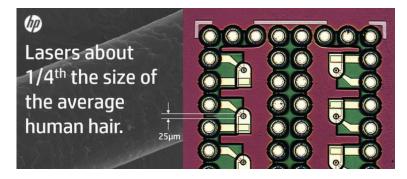

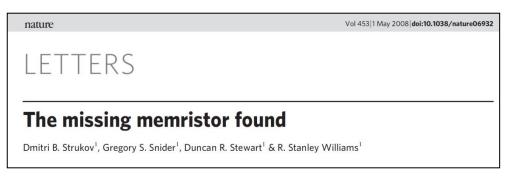

- Memristor The missing 4<sup>th</sup> element

- Predicated by Leon Chua in 1971

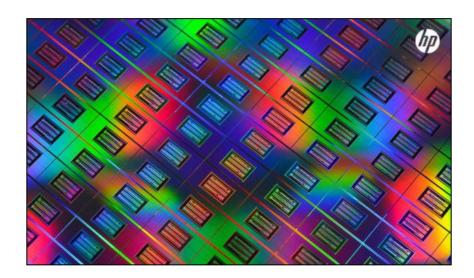

Experimentally found in 2008 at HP Lab

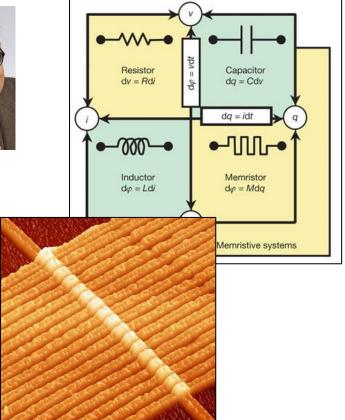

- Two principal kinds of memristors

- Change resistivity of the device, e.g. due to ion transfer

Image from http://bit-player.org/2012/ remember-the-memristor

Total memristance = sum of resistances of the doped und undoped regions

$$R_{MEM}(x) = R_{ON} \cdot x + R_{OFF} \cdot (1 - x),$$

$where \ x = \frac{w}{D} \ \epsilon \ (0, 1)$

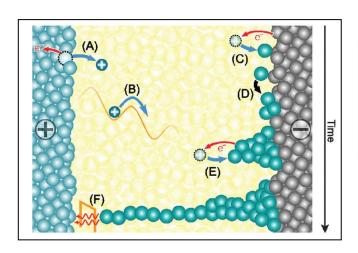

ResitiveRAM (ReRAM): Growing of a conducting filament due to depositions of cations

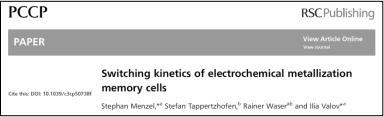

Images and equations taken from

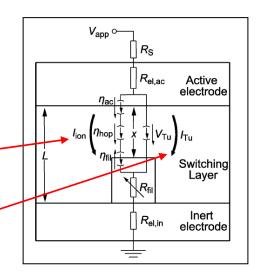

More complicated model than to the HP model before

$$I_{\text{fil,SET}} = j_{0,\text{et}} A_{\text{fil}} \left( \exp\left(-\frac{\alpha e z}{k_{\text{B}} T} \eta_{\text{fil}}\right) - 1 \right)$$

FRIEDRICH-ALEXANDER UNIVERSITY

$$I_{\mathrm{Tu}} = C \frac{3\sqrt{2m_{\mathrm{eff}}\Delta W_0}}{2x} \left(\frac{e}{h}\right)^2 \exp\left(-\frac{4\pi x}{h}\sqrt{2m_{\mathrm{eff}}\Delta W_0}\right) A_{\mathrm{fil}} V_{\mathrm{Tu}}.$$

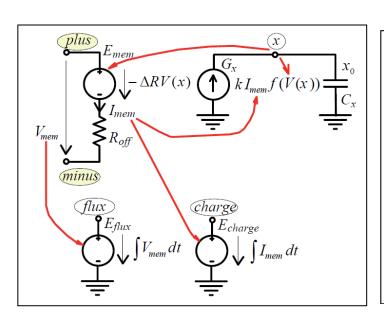

- Modelling memristor behaviour

- Used in a SPICE simulation

$$\frac{dx}{dt} = k i(t) f(x), \quad k = \frac{\mu_v R_{ON}}{D^2}$$

$$v(t) = R_{MEM}(w)i(t).$$

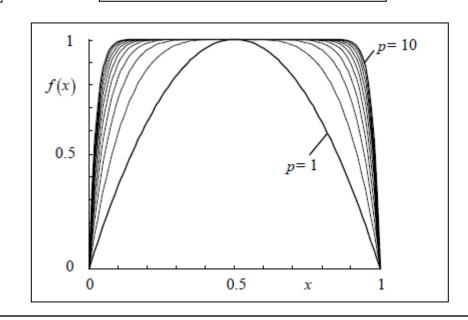

Using a model for a non-linear dopant drift (window function)

Zdeněk BIOLEK, Dalibor BIOLEK Viera BIOLKOVÁ SPICE Model of Memristor with Nonlinear Dopant Drift RADIOENGINEERING, VOL. 18, NO. 2, JUNE 2009

#### Used window function

$$f(x) = 1 - (2x - 1)^{2p}$$

- Modelling and simulating memristors

- Use an equivalent SPICE circuit model

- Simplifies execution of mixed-signal simulations

Zdeněk BIOLEK, Dalibor BIOLEK Viera BIOLKOVÁ SPICE Model of Memristor with Nonlinear Dopant Drift RADIOENGINEERING, VOL. 18, NO. 2, JUNE 2009

| * HP Memristor SPICE Model<br>* For Transient Analysis only                                                                   | * RESISTIVE PORT OF THE MEMRISTOR * **********************************                   |  |

|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|

| * created by Zdenek and Dalibor Biolek ************************************                                                   | Emem plus aux value={-I(Emem)*V(x)*(Roff-Ron)} Roff aux minus {Roff}                     |  |

| * Ron, Roff - Resistance in ON / OFF States                                                                                   | *************                                                                            |  |

| * Rinit - Resistance at T=0  * D - Width of the thin film                                                                     | *Flux computation* ***********************************                                   |  |

| * uv - Migration coefficient<br>* p - Parameter of the WINDOW-function                                                        | Eflux flux 0 value={SDT(V(plus,minus))} ***********************************              |  |

| * for modeling nonlinear boundary conditions * x - W/D Ratio, W is the actual width                                           | *Charge computation* ***********************************                                 |  |

| * of the doped area (from 0 to D)                                                                                             | Echarge charge 0 value={SDT(I(Emem))} ***********************************                |  |

| .SUBCKT memristor Plus Minus PARAMS:<br>+ Ron=1K Roff=100K Rinit=80K D=10N uv=10F p=1<br>************************************ | * WINDOW FUNCTIONS  * FOR NONLINEAR DRIFT MODELING *  ********************************** |  |

| * DIFFERENTIAL EQUATION MODELING * ***********************************                                                        | *window function, according to Joglekar .func $f(x,p)=\{1-(2*x-1)^{(2*p)}\}$             |  |

| Gx 0 x value={ $I(Emem)*uv*Ron/D^2*f(V(x),p)$ }                                                                               | *proposed window function                                                                |  |

| Cx x 0 1 IC={(Roff-Rinit)/(Roff-Ron)}                                                                                         | :.func $f(x,i,p)=\{1-(x-stp(-i))^{(2*p)}\}$                                              |  |

| Raux x 0 1T                                                                                                                   | .ENDS memristor                                                                          |  |

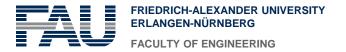

- Modelling multi-bit feature

- Demonstration in a SPICE simulation

**Architecture**

#### Outline

- Memristor technology

- Digital Boolean logic with memristors

- Ternary Computing using memristors

- Conclusion

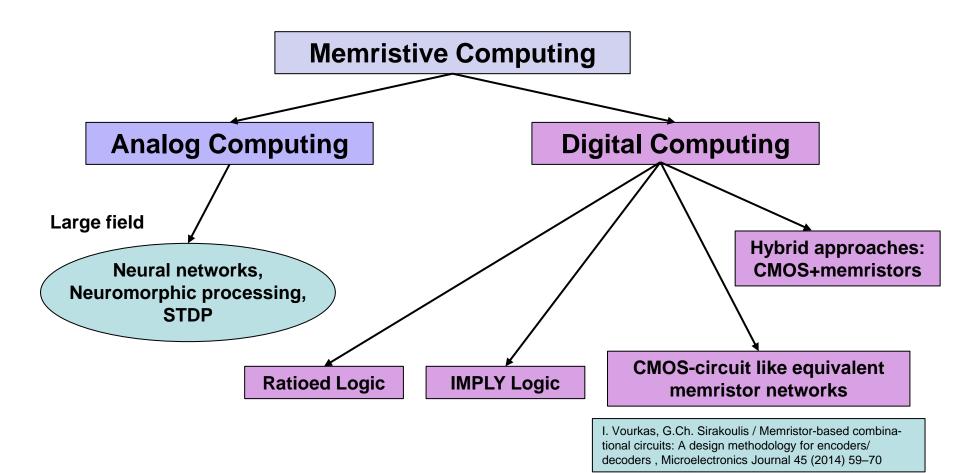

Different branches of computing with memristors

Ratioed Logic

S. KVATINSKY, N. WALD, G. SATAT, A. KOLODNY, U.C. WEISER, G.E. FRIEDMAN MRL - Memristor Ratioed Logic 13th International Workshop on CNNA, 1:6, pp. 29-31, 2012.

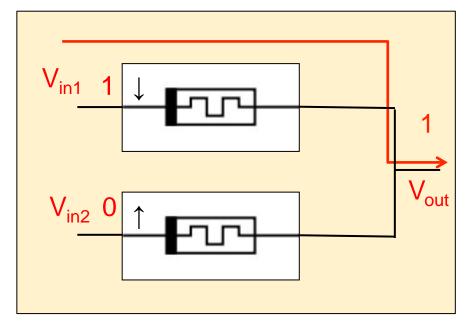

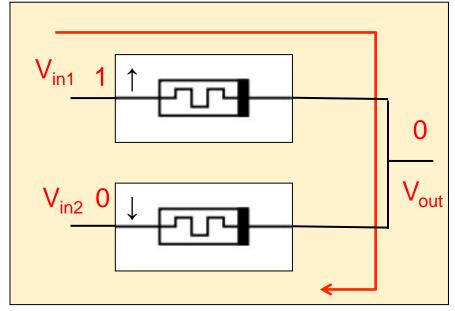

- Creating simple AND- and OR- gates by (mem)resistive networks

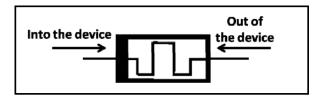

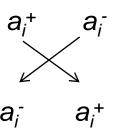

- Making following abstraction

- Current flowing into the device: memristance \u00c4

- Current flowing out of the device: memristance \

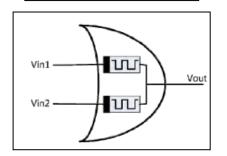

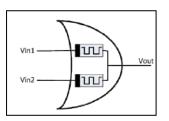

#### Structure of OR gate

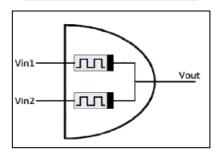

#### Structure of AND gate

Architecture

Example for OR and AND gate for input V<sub>in1</sub> = 1 and V<sub>in2</sub> = 0

FRIEDRICH-ALEXANDER UNIVERSITY

**ERLANGEN-NÜRNBERG**

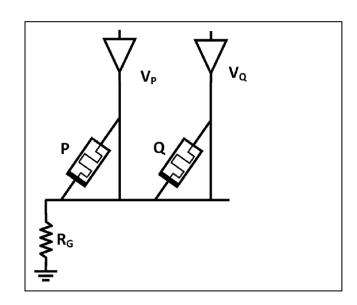

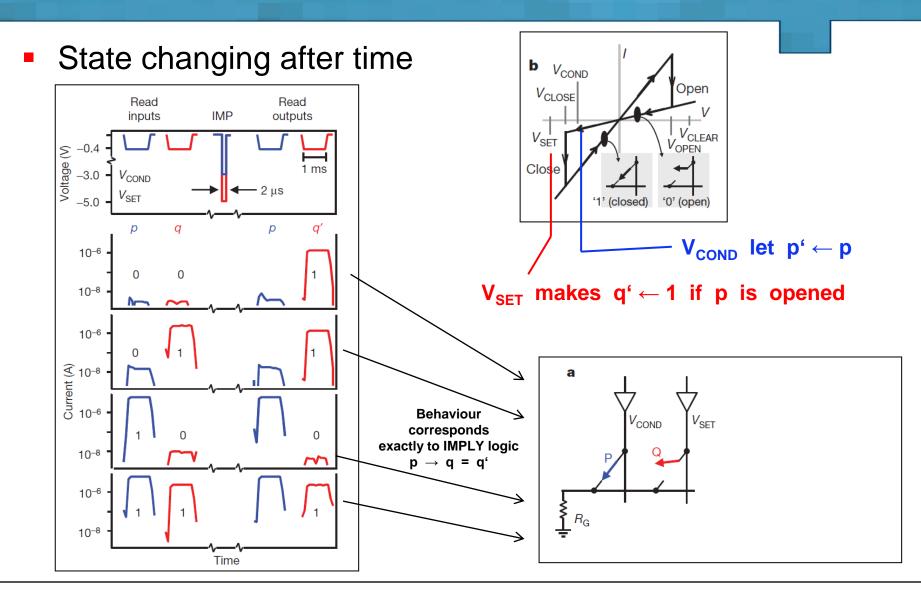

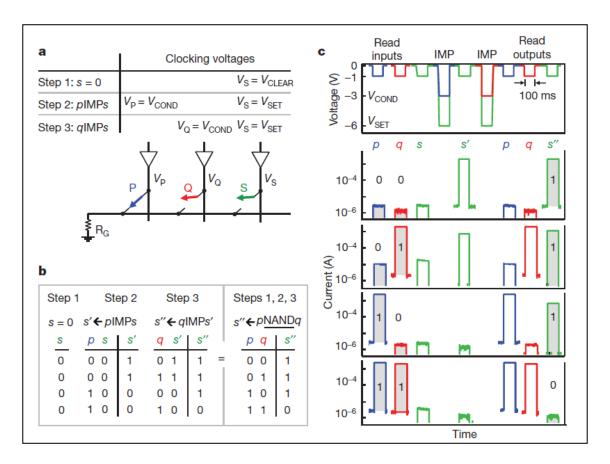

#### IMPLY Logic

- Based on conditional toggling (kind of 3-phase logic)

- Initializing certain states in memristors by input data

- Apply constant voltages (V<sub>cond</sub> and V<sub>set</sub>) that possibly change states

- Reading out the state (applying voltage that does not change states)

**ERLANGEN-NÜRNBERG**

FRIEDRICH-ALEXANDER UNIVERSITY

Can be expanded to NAND by subsequent IMP operations

**Architecture**

#### **Outline**

- Memristor technology

- Boolean logic with memristors

- Ternary Computing using memristors

- Conclusion

- Ternary computers

- Since the days of Konrad Zuse and John v. Neumann

- Binary computers

- Ternary system

- differentiates between 3 and not 2 states

http://ternary.3neko.ru/history\_of\_ternary.html

- 17<sup>th</sup> century: Caramuel y Lobkowitz

- investigated number system with digits 0, 1, and 2

- 18<sup>th</sup> century: Abraham Gotthelf Kästner

- each number weighted sum of multiples of 3

- Weights were -1, 0, and +1

- Donald Knuth

- Denoted that as balanced ternary system

- 1961: Avizienis [IRE Trans. Trans. Electron Computers]

- Fast carry-free addition with signed-digit (SD) numbers

- Difficult to implement in digital electronics

- 1988: Parhami

- Binary SD number system

- 1958: Brousentsov

FRIEDRICH-ALEXANDER UNIVERSITY

SETUN ternary computer

**ERLANGEN-NÜRNBERG**

- May be a renaissance of ternary computers?

- CMOS compatible,

- fast,

- Energy-poor,

- multi-bit storing capable non-volatile memory cells

like memristors

Hybrid CMOS-memristor approach

IOP Publishing

Semiconductor Science and Technology

Semicond. Sci. Technol. 29 (2014) 104008 (13pp)

doi:10.1088/0268-1242/29/10/104008

Using the multi-bit feature of memristors for register files in signed-digit arithmetic units

Dietmar Fev

Friedrich-Alexander-Universität Erlangen-Nürnberg (FAU), Department Computer Science 3, Chair for Computer Architecture, Martensstr. 3, 91054 Erlangen, Germany

Signed-digit number representation to base 2

$$w(a) = \sum_{i=0}^{n} a_i \cdot 2^i \qquad a = (a_{n-1}, ..., a_0), \ a_i \in \{-1, 0, 1\}$$

Example:

$$10\overline{1} = 1 \times 2^2 + 0 \times 2^1 - 1 \times 2^0 = 4 - 1 = 3$$

;  $\overline{1} = -1$

$1\overline{1}1 = 5 - 2 = 3$

$011 = 2 + 1 = 3$

Used digital coding for signed digits (SD)

| a <sup>+</sup> | a⁻ | SD       |

|----------------|----|----------|

| 0              | 0  | 0        |

| 0              | 1  | -1       |

| 1              | 0  | 1        |

| 1              | 1  | Not used |

#### Carry-free addition in O(1)

#### Binary addition

O(n)

Best case: log(n)

#### Signed digit addition

| <b>X</b> <sub>i</sub> | y <sub>i</sub> | Z <sub>i</sub> | C <sub>i+1</sub> |

|-----------------------|----------------|----------------|------------------|

| 0                     | 0              | 0              | 0                |

| 0                     | 1              | -1             | 1                |

| 1                     | 0              | -1             | 1                |

| 1                     | 1              | 0              | 1                |

| Ci | z <sub>i</sub> | Si |

|----|----------------|----|

| 0  | 0              | 0  |

| 0  | -1             | -1 |

| 1  | 0              | 1  |

| 1  | -1             | 0  |

O(1)

**ERLANGEN-NÜRNBERG**

FRIEDRICH-ALEXANDER UNIVERSITY

Addition / subtraction of (i) a SD number a and a binary number B and (ii) two SD numbers c and z

(i)

$$c_i^+ = a_i^+ \vee \left( B_i \wedge \overline{a_i^-} \right) \quad \land: \text{ and } \lor: \text{ or }$$

$$z_i^- = \left( a_i^+ \vee a_i^- \right) \oplus B_i \quad \oplus: \text{ exor}$$

(ii)

$$s_{i}^{+} = \overline{z_{i}^{-}} \wedge c_{i-1}^{+}$$

$s_{i}^{-} = \overline{c_{i-1}^{+}} \wedge z_{i}^{-}$

a – B: Subtraction can be simply reduced to addition

$$a - B = (-1) \cdot ((-1) \cdot a + B)$$

Negative complement simply by exchange positive and negative part

Architecture

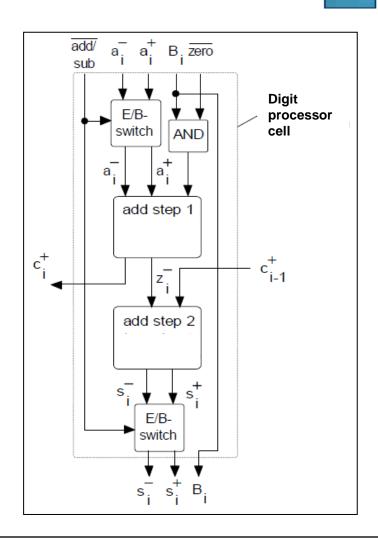

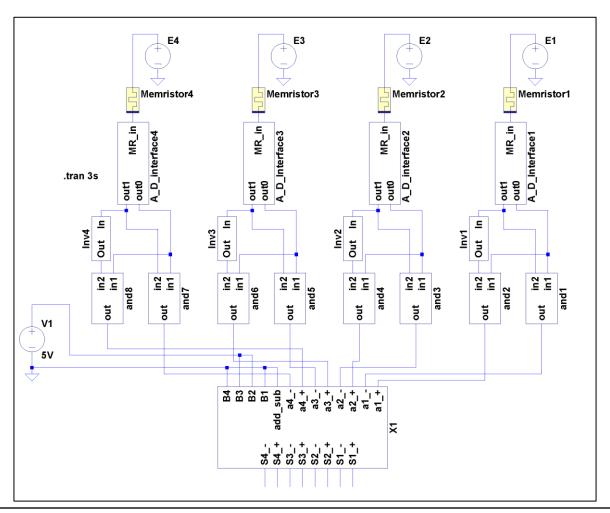

Schematic of a digit processor cell

## 2 Signed-digit (SD) arithmetic

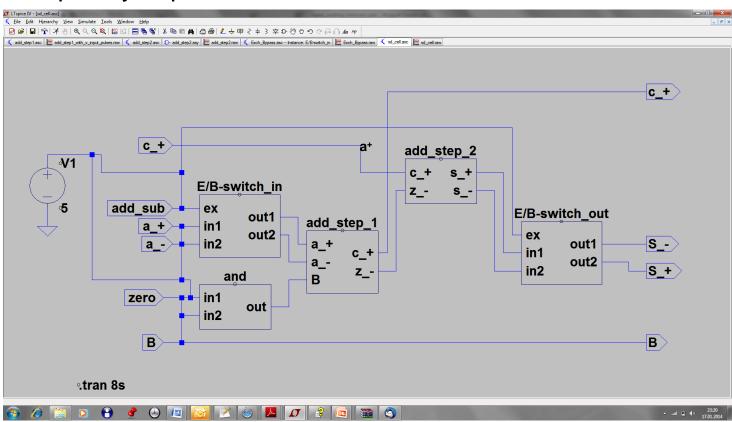

- Corresponding gate logic for an SD adder / subtractor cell

- Completely implemented in SPICE

**Architecture**

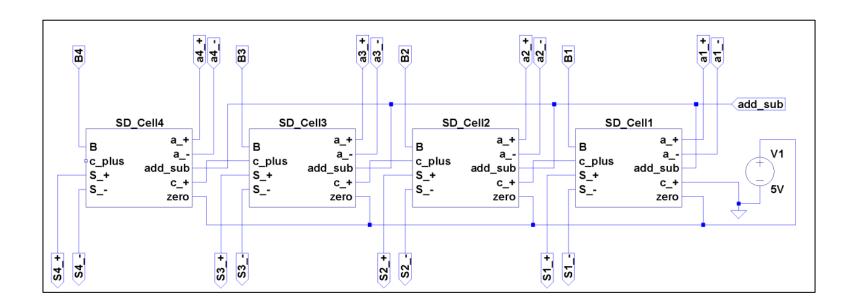

- Schematic of a digit processor cell

- Several cells are connected side-by-side to a row

**Architecture**

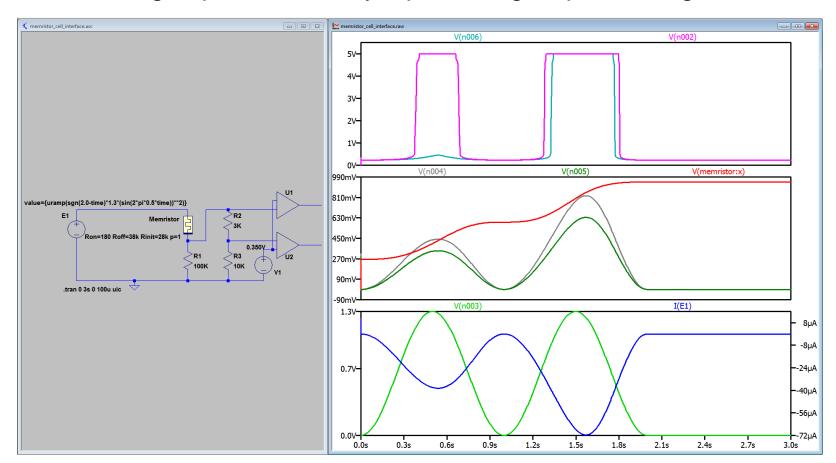

- Modelling multi-bit feature

- Interfacing to produce binary input for digital processing circuit

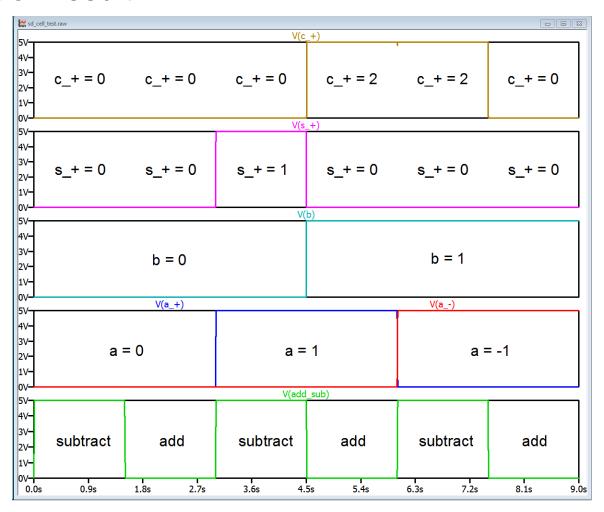

Memristor-based SD arithmetic unit

#### Simulation result

#### Conclusion

- Possible computer architecture revolution happens?

- Core technology are NVM like memristors

- Proposal for first memristive Boolean logic gates

- Renaissance or break-through for ternary computers

- Outlook

- First simple gates have to be realised

- Devices have to be improved

- From gates to complex systems