### **FEM Modeling for PCB Assembly Simulation**

Ming-Hsiao Lee, Jiunn-Horng Lee, Chih-Min Yao, Jen-Gaw Lee

National Center for High-performance Computing National Applied Research Labs, Taiwan Email: 9303103@narlabs.org.tw

### Resume

#### **CURRENT POSITION/INSTITUTION**

**Research Fellow, National Center for High Performance Computing (NCHC), National Applied Research Laboratories, Taiwan**

**EDUCATION** National Tsing Hua University, Taiwan, Dept. of Mechanical Engineering, PHD.

#### **RESEARCH FIELDS**

- Solid mechanics, numerical simulation.

- Numerical methods, mesh generation, meshless method.

- 3D printing, PCBA deformation simulation, bio-mechanical simulation.

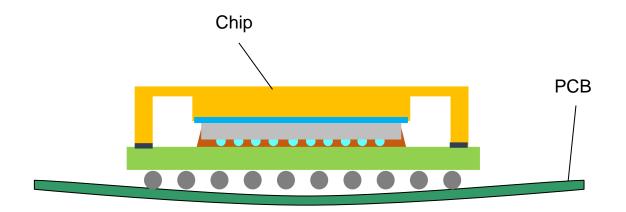

### PCBA Warpage Problems Induced by Thermal Mismatch during Temperature Change

Induced by the unevenly distribution of copper circuits, multimaterialled components

- •Causes:

- ➢Solder opens

- Stress concentration

- ➤Shorter fatigue life

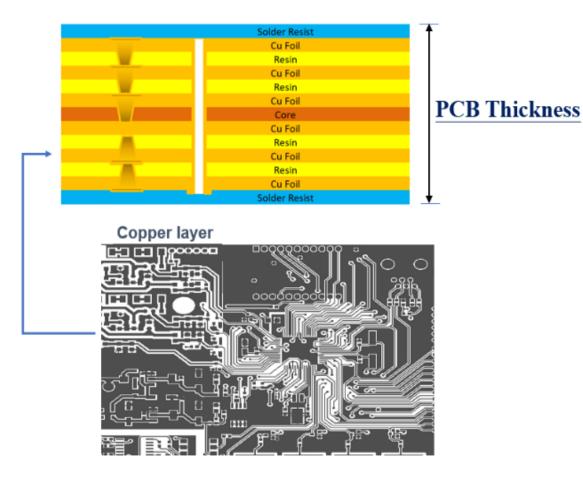

### **PCB Stack-Up**

4

## **Difficulties with Multi-scaled Problems**

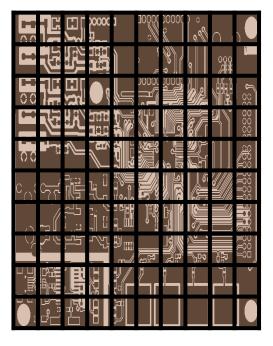

### Circuit traces are too tiny

- Impossible to directly model the circuit traces

- The scale of circuit traces is much smaller than that of PCB boards

- Solid element models will be too big for simulation

### Non-even distribution of circuit traces

Composite material properties are different at different locations

## Trace Mapping

| <br> |  |  |

|------|--|--|

|      |  |  |

|      |  |  |

|      |  |  |

|      |  |  |

|      |  |  |

#### Ratio of copper area

| 1. | 1. | 1. | 0. | 0. | 0. |

|----|----|----|----|----|----|

| 1. | 1. | 1. | 0. | 0. | 0. |

| 1. | 1. | 1. | 0. | 0. | 0. |

| 0. | 0. | 0. | 0. | 0. | 0. |

| 0. | 0. | 0. | 0. | 0. | 0. |

| 0. | 0. | 0. | 0. | 0. | 0. |

(6 x 6)

(5 x 5)

| 1. | 1. | .5  | 0. | 0. |

|----|----|-----|----|----|

| 1. | 1. | .5  | 0. | 0. |

| .5 | .5 | .25 | 0. | 0. |

| 0. | 0. | 0.  | 0. | 0. |

| 0. | 0. | 0.  | 0. | 0. |

6

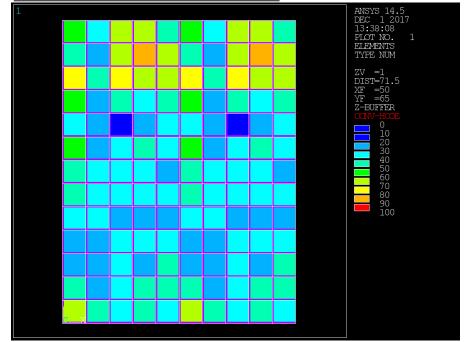

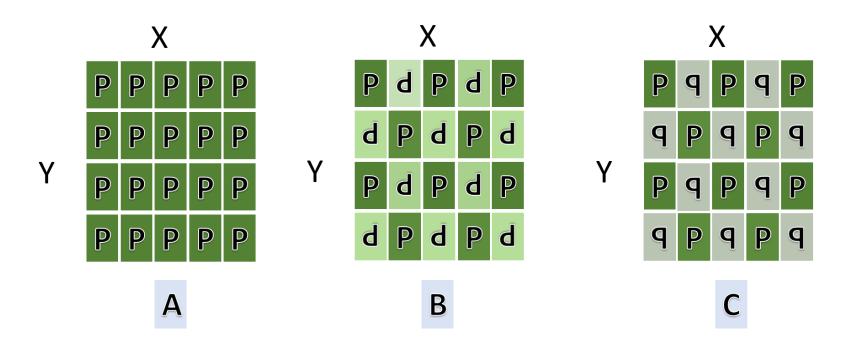

### **Trace Mapping**

#### Area ratio of copper

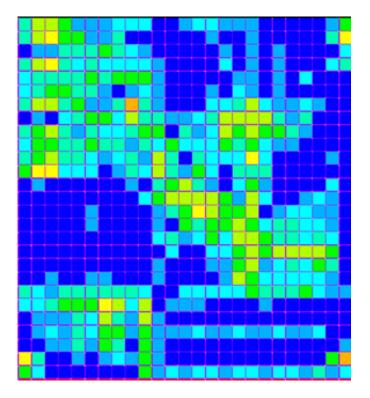

### **Trace Mapping**

#### Area ratio of copper

#### **Irregular Mapping**

### **Regular Mapping**

# Equivalent Young's Modulus & CTE

- Effective material property  $\alpha_{IJK}$  for element IJ on layer K is then computed as:

- (1)  $\alpha_{IJK} = (\delta / 100) * \alpha_{metal} + (1 \delta / 100) * \alpha_{ep}$  for copper layers

- (2)  $\alpha_{IJK} = \alpha_{dielectric}$  for dielectric layers

- Where  $\alpha$  is:

- Co-efficient of thermal expansion

- Young's modulus of elasticity

## Equivalent Young's Modulus

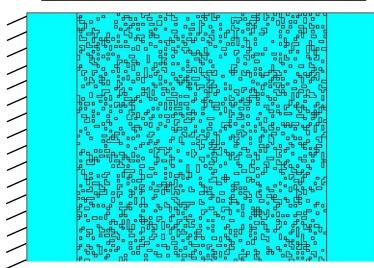

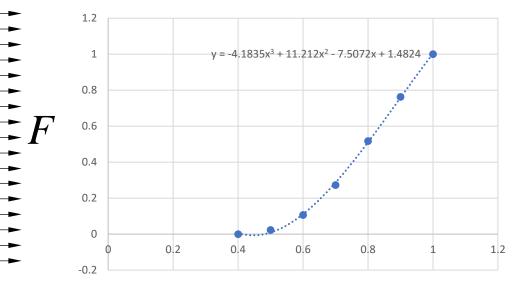

#### **Randomly-distributed copper**

Subjected to a tensile load

$$\sigma = E\varepsilon$$

$$\frac{F}{A} = E \frac{d}{l} >> E = \frac{Fl}{Ad}$$

Equivalent Young's Modulus

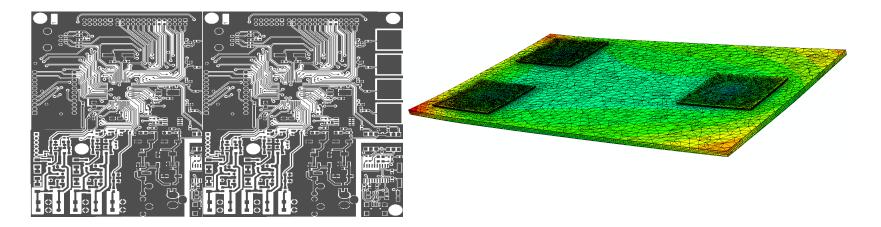

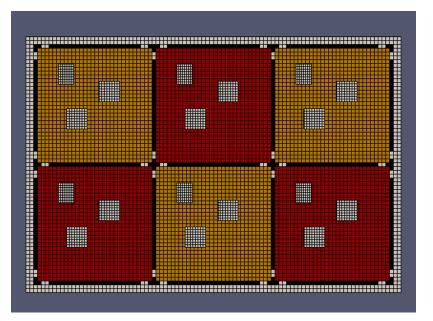

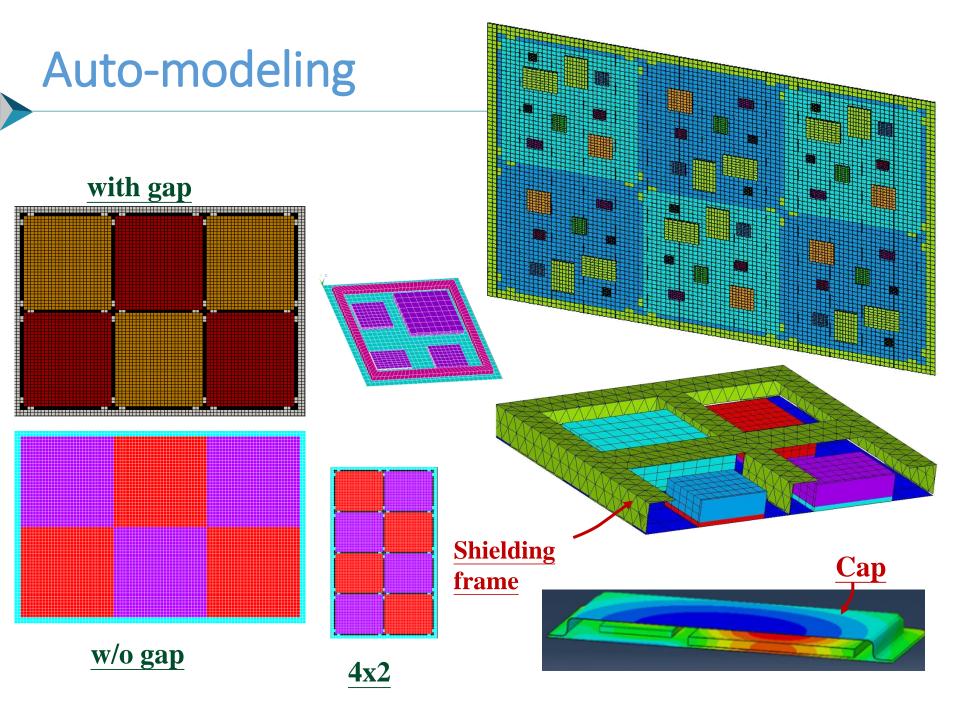

### Panel arrangement

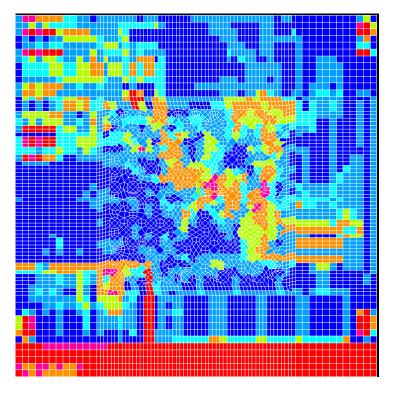

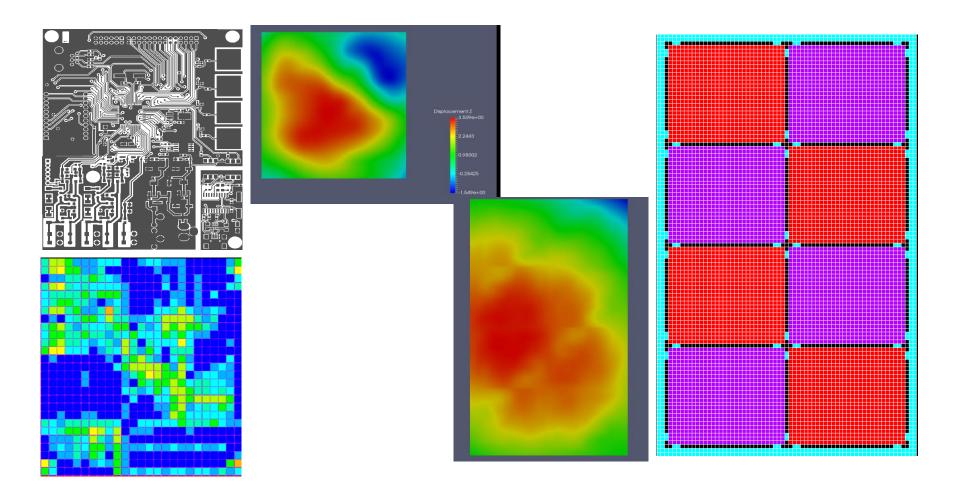

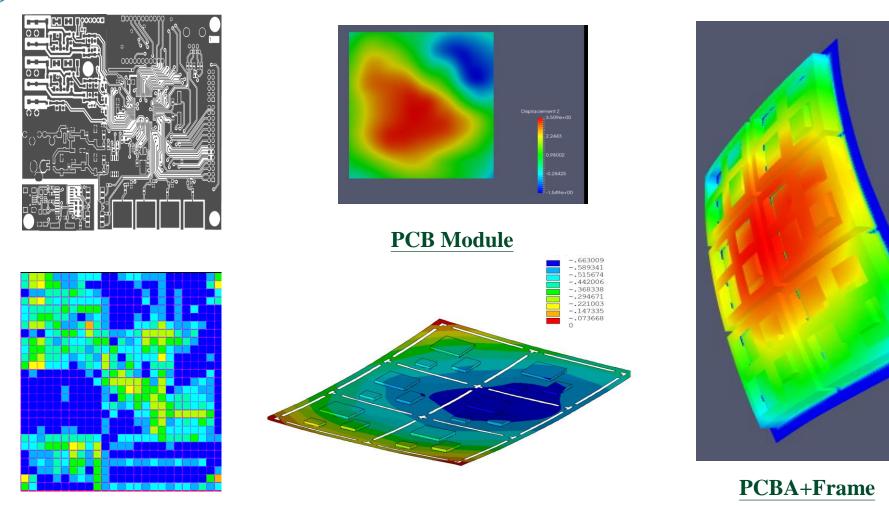

### PCB Analysis : Module & Panel

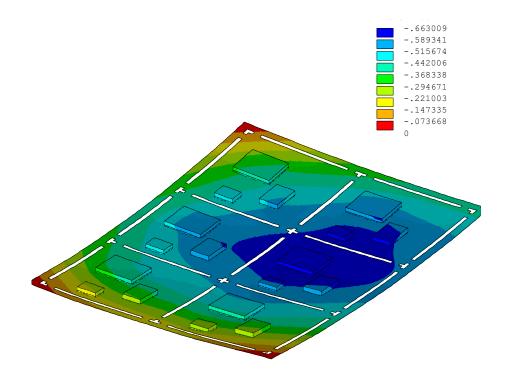

## PCBA (PCB+Chips) for SMT Process

### PCB+PCBA Warpage:

97.0 μm

103.3 µm

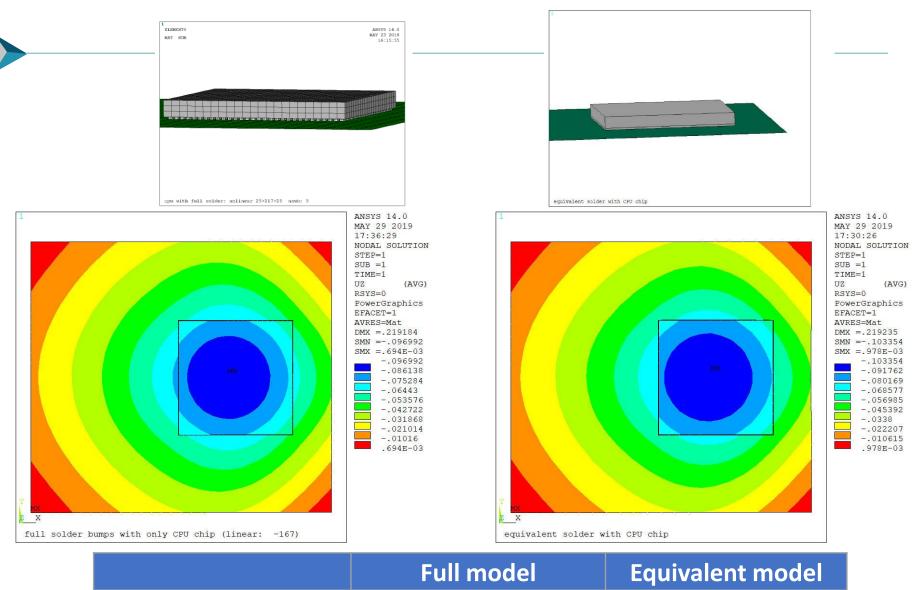

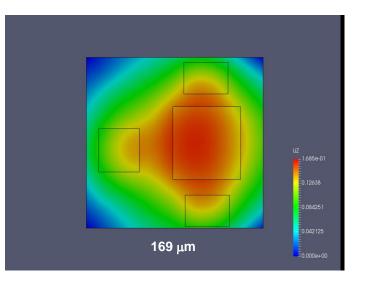

### Verification case:

|                    | Simulation<br>(µm) | Experiment<br>(µm) |

|--------------------|--------------------|--------------------|

| Maximum<br>Warpage | 169                | 140                |

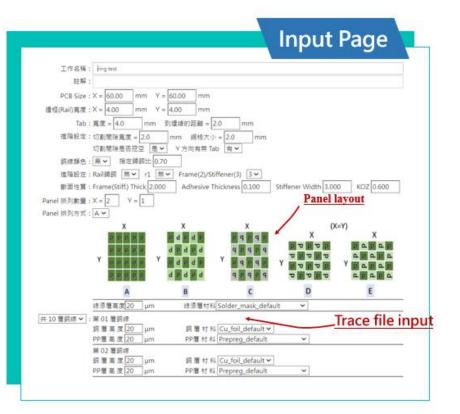

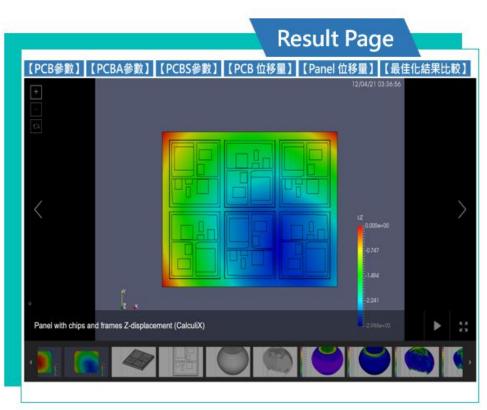

# Web-based Simulation Platform

### Conclusions

- PCB or PCBA simulation is a multi-scaled problem

- With the proposed effective modeling method, the PCB/PCBA warpage simulation becomes feasible with a reasonable computing resources

- The simulation of the PCB/PCBA manufacturing process based on the effective modeling method becomes easy to implement